Product Summary

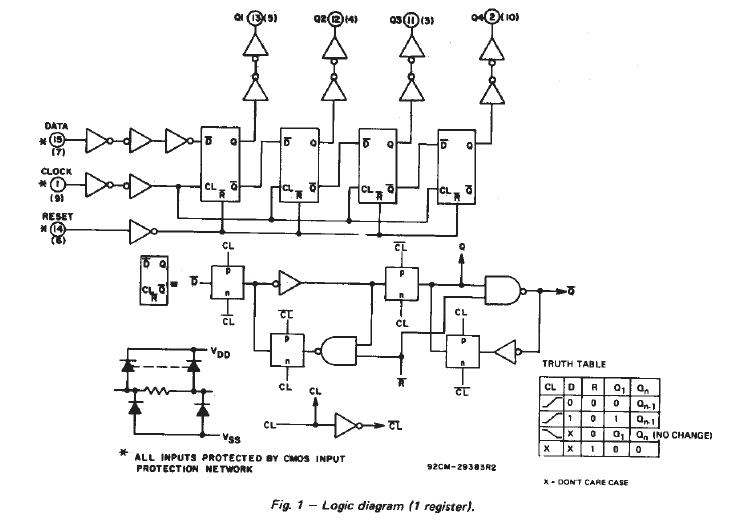

The CD4015 is a CMOS dual 4-stage static shift register. It consists of two identical, independent; 4-stage serial-input/parallel output registers. The CD4015 is supplied in 16-lead hermetic dual-in-line ceramic package, 16-lead dual-in-line plastic package, 16-lead small-outline package, and 16-lead thin shrink small=outline packages. The applications of the CD4015 include serial-input/parallel-output data queueing, serial to parallel data conversion and general purpose register.

Parametrics

CD4015 absolute maximum ratings: (1)voltages referenced to VSS terminal: -0.5V to +20V; (2)input voltage range, all inputs: -0.5V to VDD+0.5V; (3)DC input current, any one input: ±10mA; (4)power dissipation per package (PD), for TA=-55℃ to +100℃: 500mW; for TA=+100℃ to +125℃: derate linearity at 12mW/℃ to 220mW; (5)device dissipation per output transistor, for TA=full package-temperature range (all package types): 100mW; (6)operating-temperature range (TA): -55 to +125℃; (7)storage temperature range, Tstg: -85 to +150℃; (8)lead temperature, during soldering:, at distance 1/16±1/32 inch (1.59±0.79mm) from case for 10s max: +265℃.

Features

CD4015 features: (1)medium speed operation: 12MHz typ clock rate at VDD-VSS=10V; (2)fully static operation; (3)8 master-slave flip-flops plus input and output buffering; (4)100% tested for quiescent current at 20V; (5)5V, 10V, and 15V parametric ratings; (6)standardized, symmetrical output characteristics; (7)maximum input current of 1μA at 18V over full package-temperature range; (8)noise margin (full package-temperature range)=1V at VDD=5V; 2V at VD=10V; 2.5V at VDD=15V; (9)meets all requirements of JEDEC tentative standard No.13, standard specifications for description of B series CMOS devices.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CD4015BCM |

Fairchild Semiconductor |

Counter Shift Registers Dl 4-Bit Shift Reg |

Data Sheet |

Negotiable |

|

||||||||||||

|

CD4015BCN |

Fairchild Semiconductor |

Counter Shift Registers Dl 4-Bit Shift Reg |

Data Sheet |

Negotiable |

|

||||||||||||

|

CD4015BM96E4 |

Texas Instruments |

Counter Shift Registers CMOS Dual 4-Stage Static Shift Reg |

Data Sheet |

|

|

||||||||||||

|

CD4015BM96G4 |

Texas Instruments |

Counter Shift Registers CMOS Dual 4-Stage Static Shift Reg |

Data Sheet |

|

|

||||||||||||

|

CD4015BPWR |

Texas Instruments |

Counter Shift Registers Dual 4-Stage Static |

Data Sheet |

|

|

||||||||||||

|

CD4015BPW |

Texas Instruments |

Counter Shift Registers CMOS Dual 4-Stage Static Shift Reg |

Data Sheet |

|

|

||||||||||||

|

CD4015BNSR |

Texas Instruments |

Counter Shift Registers CMOS Dual 4-Stage Static Shift Reg |

Data Sheet |

Negotiable |

|

||||||||||||

|

CD4015BNSRG4 |

Texas Instruments |

Counter Shift Registers CMOS Dual 4-Stage Static Shift Reg |

Data Sheet |

Negotiable |

|

||||||||||||

(Hong Kong)

(Hong Kong)